Scritto da Prof. S. Giannitto - Amministratore 01/12/2010 Scritto da Prof. S. Giannitto - Amministratore 01/12/2010 |

| Totale Visite: 6420 |

| |

|

|

A marzo, i ricercatori IBM avevano annunciato la realizzazione di chip in grado di comunicare con impulsi luminosi anzich� segnali elettrici. Questi Nanophotonic Avalanche Photodetector (NAP) sono pi� veloci e si pongono come evoluzione importante verso il raggiungimento di una migliore efficienza energetica computazionale, con implicazioni significative per il futuro dell'elettronica.

Questo traguardo � stato raggiunto grazie al passaggio dall'elettronica standard a quella fotonica. I materiali utilizzati invece sono abbastanza comuni: il NAP � costituito infatti da silicio e germanio, lavorati, a basso costo, con normali processi di fabbricazione tipici dei semiconduttori.

Qualche giorno fa, negli stessi laboratori di IBM, i ricercatori svelano una nuova tecnologia per chip, che integra dispositivi elettrici e ottici sulla stessa basetta di silicio. IBM spera cos� di spingere verso i sistemi di Exascale computing, in modo che i chip siano in grado di eseguire milioni di trilioni di calcoli al secondo.La nuova tecnologia � chiamata CMOS Integrated Silicon Nanophotonics, e offre un'alta densit� di integrazione dei singoli componenti ottici su un unico chip.

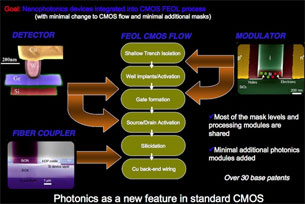

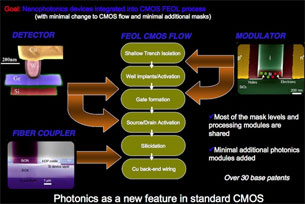

I device cos� prodotti hanno una grande capacit� di low-loss e un'elevata ampiezza di banda dati. Inoltre, poich� i framework CMOS sono comuni, il prezzo di questa tecnologia � piuttosto contenuto. Infatti, come ha spiegato Solomon Assefa in un'intervista per ZDNet UK, i chips che utilizzano la tecnologia CMOS possono essere prodotti nelle fonderie di semiconduttori esistenti, aggiungendo solo un paio di moduli di elaborazione a un flusso standard di fabbricazione CMOS, come mostra questa immagine, estrapolata dalla pubblicazione illustrativa di IBM:

In questo modo IBM � convinta di aver sorpassato la concorrenza, e in particolar modo Intel: Assefa spiega infatti che la principale differenza fra la tecnologia IBM e quella concorrente sta nel fatto che Intel ha messo in cantiere chip CMOS e chip nanofotonici, mentre IBM integra entrambi su un unico pezzo di silicio.

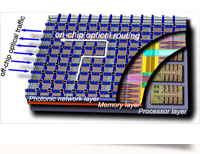

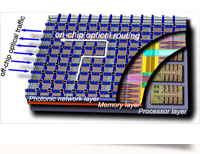

Come si pu� leggere (e un po' fantasticare) nell'annuncio ufficiale, il chip 3D del futuro sar� costituito da diversi strati collegati tra loro da fitti fori: lo strato inferiore sar� esso stesso un processore, dotato di molte centinaia di core; lo strato di memoria (o strati) si trover� in cima e fornir� un rapido accesso alle cache locale; sullo stack invece sar� allocato lo strato fotonico con molte migliaia di singoli dispositivi ottici e circuiti elettrici analogici. Quest'ultimo strato giocher� un ruolo fondamentale per fornire un'ampia larghezza di banda tra core e traffico off-chip e per regolare il traffico dati grazie a una serie di interruttori nanofotonici.

L'obiettivo finale di questo progetto � dicono gli addetti ai lavori � � di sviluppare una tecnologia per l'integrazione on-chip dei circuiti nanofotonici ultra-compatti per la manipolazione dei segnali luminosi, analogamente al modo in cui i segnali elettrici vengono manipolati nei chip dei computer.

Questa tecnologia segue la tendenza attuale dei sistemi di calcolo ad alte prestazioni, che aumenta il parallelismo di elaborazione a tutti i livelli utilizzando multithread, aumentando il numero di chip in rack e blade, il numero di core in un chip. E' pensabile che essa trovi utile impiego nei centri di elaborazione dei dati, in quanto le comunicazioni ottiche garantiscono importanti capacit� di calcolo ed elevato parallelismo.

Visualizza il file in formato PDF

|